### La loi de convexité énergie-fréquence de la consommation des programmes : modélisation, thermosensibilité et applications

Karel de Vogeleer

#### ► To cite this version:

Karel de Vogeleer. La loi de convexité énergie-fréquence de la consommation des programmes : modélisation, thermosensibilité et applications. Informatique [cs]. Telecom ParisTech, 2015. Français. NNT : . tel-01258577

### HAL Id: tel-01258577 https://minesparis-psl.hal.science/tel-01258577

Submitted on 19 Jan 2016  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

## **TELECOM ParisTech**

Spécialité « Informatique et Réseaux » présentée et soutenue publiquement par

### **Karel De Vogeleer**

4 Septembre 2015

### La loi de convexité énergie-fréquence de la consommation des programmes : modélisation, thermosensibilité et applications

Co-Directeur de la thèse : Gérard MEMMI Co-Directeur de la thèse : Encadrant de la thèse : Fabien COELHO

**Pierre JOUVELOT**

Jury

M. Maurice GAGNAIRE, Prof., TELECOM ParisTech M. William JALBY, Prof., Université de Versailles Saint-Quentin-en-Yvelines M. Georg HAGER, Dr. rer. nat. habil., Friedrich-Alexander Uni Erlangen-Nürnberg M. Christophe GUETTIER, Dr., SAGEM

Examinateur Rapporteur Rapporteur Examinateur

## The Energy/Frequency Convexity Rule of Energy Consumption for Programs: Modeling, Thermosensitivity and Applications

Karel De Vogeleer

## Abstract

Both theoretical and experimental evidence is presented in this work for the existence of an Energy/Frequency Convexity Rule, which relates energy consumption and microprocessor frequency for nanometer-scale microprocessors. Typical nanometer-scale application processors were monitored running specific compute-intensive kernels using high-resolution power gauges. Data gathered during several week-long acquisition campaigns suggest that energy consumed is strongly correlated with the microprocessor's frequency, and, more interestingly, the curve exhibits a clear minimum over the processor's frequency range. An analytical model for this behavior is provide and motivated, which fits well with the data. The circumstances are discussed under which this convexity rule can be exploited, and when other methods are more effective, with the aim of improving the microprocessor's energy efficiency. The Energy/Frequency Convexity Rule is potentially more exploitable by low-power systems, such as battery-powered and embedded systems, and less likely by high-performance computer systems. The Energy/Frequency Convexity Rule is also applied to multi-buddy systems, Amdahl's law and heterogeneous computing.

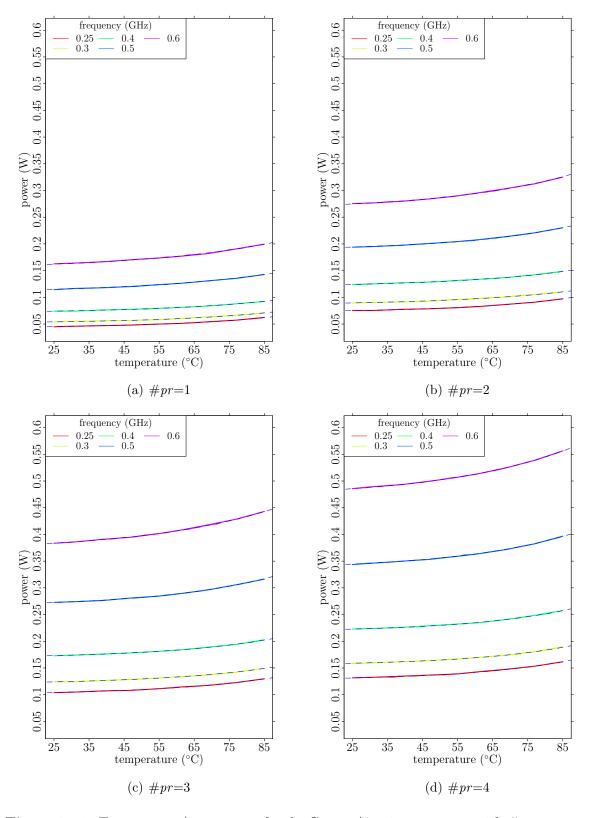

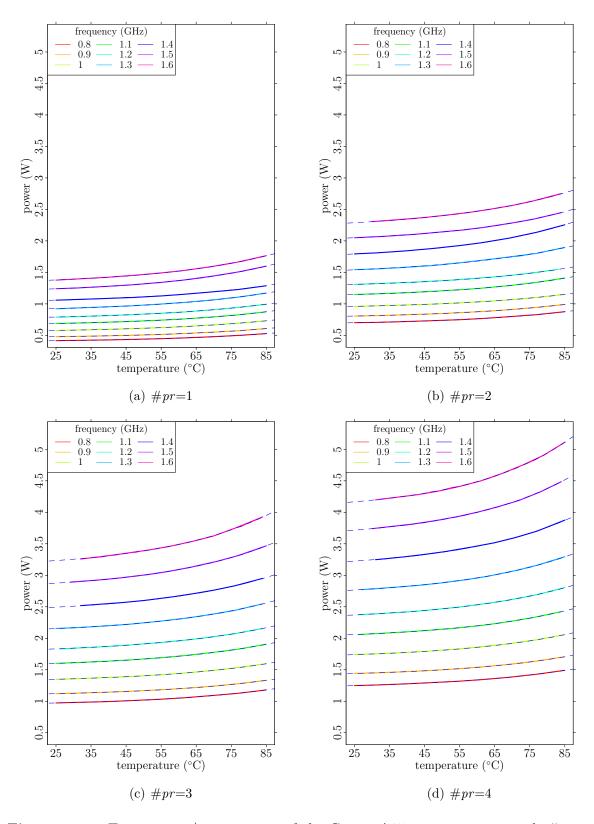

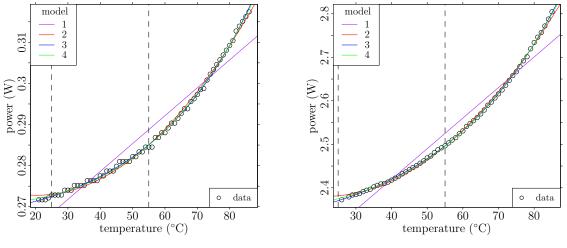

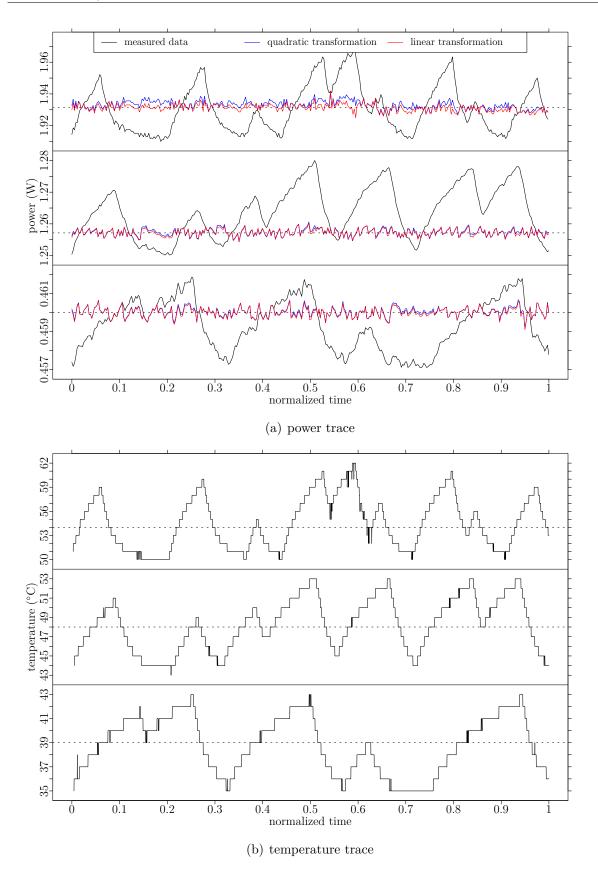

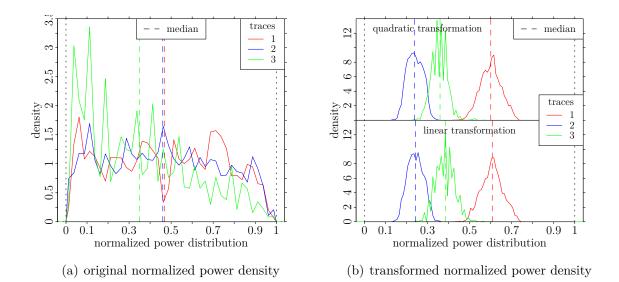

Given that the microprocessor's energy consumption is temperature-dependent, a macro-level temperature/power relationship for application processors is introduced and experimentally validated. By adopting a holistic view, this model is able to take into account many of the physical effects that occur within such systems. Via measurements on two pertinent platforms sporting nanometer-scale application processors, it is shown that the power/temperature relationship is indeed very likely exponential over a 20°C to 85°C temperature range. The data suggest that, for a temperature range between 20°C and 55°C, a quadratic model is still accurate and a linear approximation is acceptable. Power transformation models are also presented that aim at canceling the temperature biases in power traces. These transformation models are developed to increase the accuracy and meaningfulness of power measurement traces.

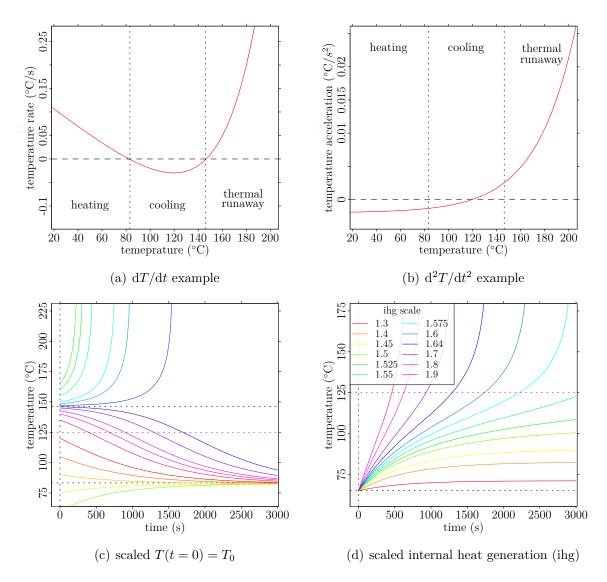

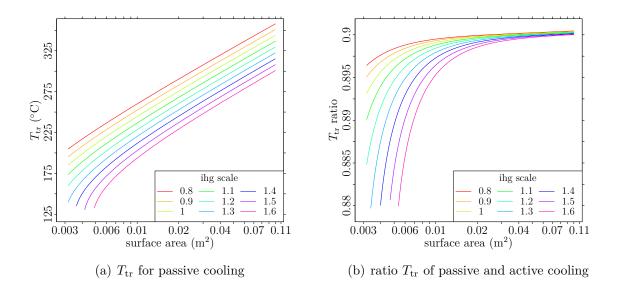

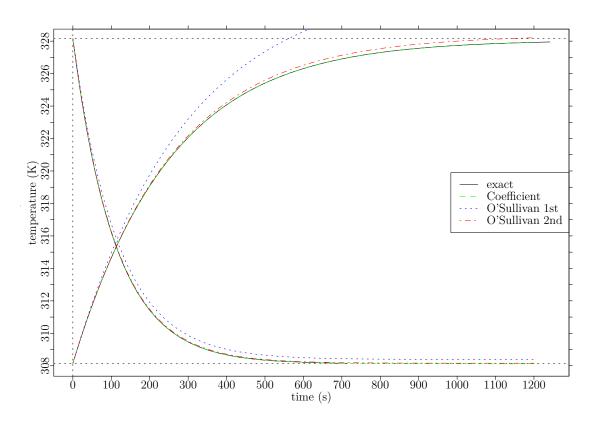

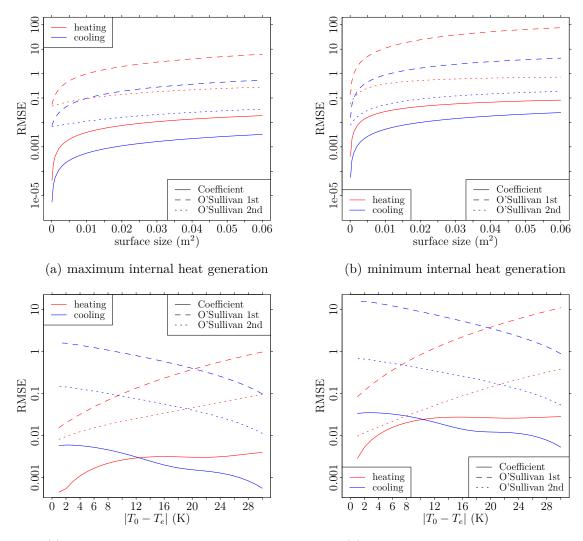

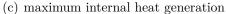

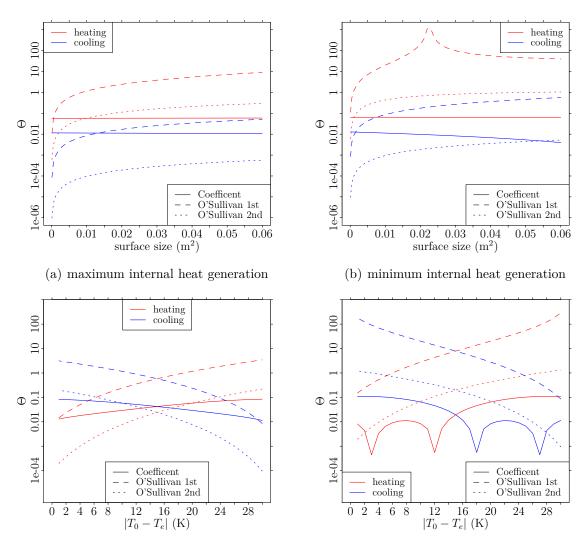

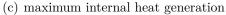

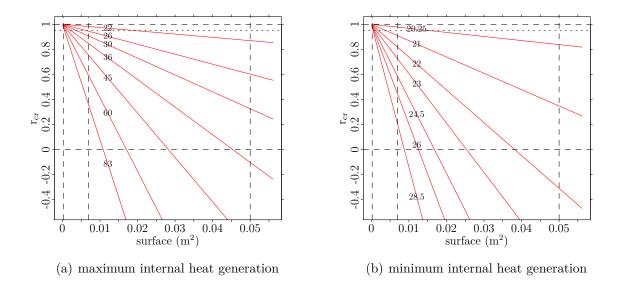

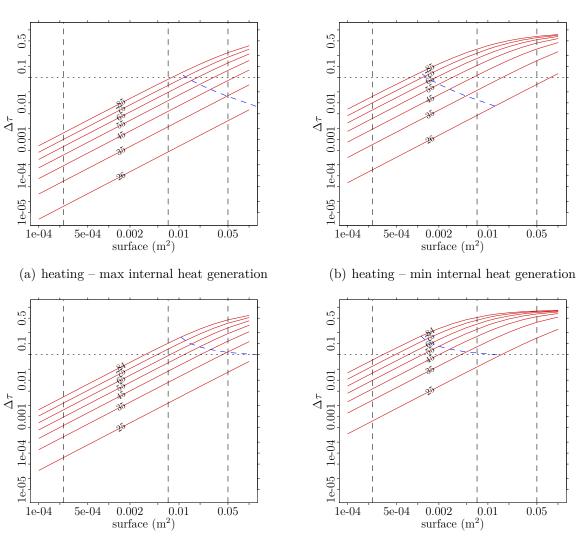

Besides static power measurements, the transient power and thermal behavior are also analyzed by means of the cooling laws and the temperature/power relationship models. Exponential cooling models are justified for actively-cooled microprocessors. For passively cooled processors however, as frequently found in embedded systems, an exponential law may not be theoretically justified. Here, the tractability of the exact cooling law for a passively-cooled body is analyzed, subject to radiative cooling and a modest level of heat loss via convection. Focusing then on embedded microprocessors, the performance difference between the new passive cooling law and the conventionally-used exponential one is compared. It is shown that, for large surface sizes, the radiative cooling component can be comparable to the convective cooling one. However, for large cooling surface areas of the order of  $10 \text{ cm}^2$  or more, it is shown that the differences between the passive cooling law and the exponential cooling law are significant. The results thus suggest that, in the absence of accurate temperature measurements, an exponential cooling law is only accurate enough for small-sized SoC systems that require low processing overhead.

## Résumé

Cette these s'intéresse à la consommation énergétique d'un système embarqué durant l'execution d'un programme. Une preuve théorique est présentée dans cette thèse et expérimentale de l'existence d'une loi de convexité énergie-fréquence de la consommation des programmes, qui concerne la consommation d'énergie et la fréquence des microprocesseurs à l'échelle nanométrique. Des noyaux de calcul intensif spécifiques ont été exécutés sur des processeurs d'applications typiques, à l'échelle nanométrique, et leurs caractéristiques mesurées en utilisant des capteurs de puissance à haute résolution. Les données recueillies lors de nombreuses campagnes d'acquisition de données longues de plusieurs semaines chacune suggèrent que la consommation est fortement corrélée avec la fréquence du microprocesseur et, ce qui est extrêmement intéressant, que la courbe présente un minimum clair sur la gamme de fréquences utilisables sur les processeurs. Un modèle analytique de ce comportement est fourni et motivé; il cadre particulièrement bien avec les données. Les circonstances dans lesquelles cette règle de convexité peut être exploitée sont discutées, en particulier dans le but d'améliorer l'efficacité énergétique du microprocesseur. La loi de convexité énergie-fréquence de la consommation des programmes est potentiellement plus exploitable par les systèmes de faible puissance, tels que les systèmes embarqués et alimentés par piles ou batteries, et moins susceptible de l'être par les systèmes informatiques de haute performance. La loi de convexité énergiefréquence de la consommation des programmes est également appliquée aux systèmes multi-coeurs, à la loi d'Amdahl et aux systèmes informatiques hétérogènes.

Etant donné que la consommation d'énergie du microprocesseur dépend de sa température, une relation température/puissance au niveau macro pour les processeurs d'application est également introduite et validée expérimentalement dans cette thèse. En adoptant une vision holistique, ce modèle est capable de prendre en compte de nombreux effets physiques qui se produisent dans de tels systèmes. Via des mesures sur deux platesformes pertinentes comportant des processeurs d'applications à l'échelle nanométrique, il est montré que la relation puissance/température se comporte de manière exponentielle entre 20°C et 85°C. Les données suggèrent de plus que, pour une plage de températures comprise entre 20°C et 55°C, un modèle quadratique est toujours suffisamment précis et qu'une approximation linéaire est même acceptable. Des modèles de transformation d'énergie visant à annuler les biais liés à la température dans les mesures de puissance sont également présentés. Ces modèles de transformation ont été mis au point afin d'augmenter la précision et la pertinence des traces de mesure de puissance.

Outre les mesures statiques de puissance, les comportements transitoires en puissance et température sont également analysés à l'aide des lois de refroidissement et des modèles température/puissance. Il s'avère que des modèles de refroidissement exponentiels sont justifiés pour des microprocesseurs refroidis de manière active. Cependant, pour les processeurs refroidis passivement que l'on trouve fréquemment dans les systèmes embarqués, une loi exponentielle ne peut pas être justifiée théoriquement. En conséquence, la loi exacte de refroidissement pour un corps à refroidissement passif est analysée, sous condition de refroidissement radiatif et d'un niveau modeste de perte de chaleur par convection. Si l'on se concentre sur les microprocesseurs embarqués, il y a une différence de performance entre la nouvelle loi de refroidissement passif et celle, exponentielle, classiquement utilisée. On montre que, pour les grandes surfaces, le refroidissement par rayonnement peut être comparable à celui lié à la convection. Toutefois, pour les grandes surfaces de refroidissement de l'ordre de 1 dm<sup>2</sup> ou plus, les différences entre la loi de refroidissement passif et la loi exponentielle de refroidissement sont importantes. Ces résultats suggèrent donc que, en l'absence de mesures précises de la température, une loi exponentielle de refroidissement précise que pour les petits systèmes SoC ne nécessitant qu'une faible charge de traitement.

## Acknowledgements

I would like to show much appreciation and gratitude to my doctoral advisors and supervisors. Gerard Memmi's wisdom extends far beyond the particular research field handled in this work. He always had interesting comments and insight to share that greatly improved this work. I also thank him for the administrative support during my years at TELECOM ParisTech. Pierre Jouvelot's experience and scientific expertise made this work more valuable. We also had many non-work related conversations in the park, or at the school's premises, that were inspiring and amusing. Gerard and Pierre devoted significant amounts of time in shaping me as a researcher, which I appreciate vastly. Fabien Coelho I also like to thank for his comments and contributions to this work. I also like to thank the reviewers of my thesis, William Jalby and Georg Hager, for their comments and expertise.

Even tough I resided most of the time at TELECOM ParisTech's premises, I also visited CRI at MINES ParisTech in Fontaintebleau on a regular basis, where Pierre and Fabien are based. I thank the whole staff there, notably Francois Irigoin, for being open, welcoming and supportive to collaboration between institutes.

I also thank the people at the department of Biosystems Engineering of Ghent University who provided support for a part of this work. I had a great pleasure the time I stayed there, and the faculty was always helpful.

In fact, I started my doctoral studies in Sweden at Blekinge Institute of Technology, before I came to Paris. I made good friends there throughout the years. Thanks goes out also to my former supervisors there.

Last, but not least, I appreciate the support of my family too, during my Ph.D studies. The distance created by studying/working abroad is not always easy for the family. In particular, I want to wish the best of luck to my sister, who is also perusing a doctoral degree. My greatest fear was that she would graduate before me. I curbed this threat nicely.

> Karel De Vogeleer, Paris, France December, 2015

## Contents

| 1 | Introduction |                                                            |        |  |

|---|--------------|------------------------------------------------------------|--------|--|

|   | 1.1          | Summary                                                    | 3      |  |

|   | 1.2          | Contributions                                              | 6      |  |

|   | 1.3          | Outline                                                    | 7      |  |

|   | 1.4          | List of Publications                                       | 7      |  |

| 2 | Bac          | kground on Electrical Energy Consumption and Heat Transfer | 9      |  |

| - | 2.1          | Power Consumption of Computer Systems                      | 9      |  |

|   |              |                                                            | 10     |  |

|   |              | 1                                                          | 11     |  |

|   |              |                                                            | $12^{$ |  |

|   |              |                                                            | 13     |  |

|   |              |                                                            | 15     |  |

|   |              |                                                            | 16     |  |

|   | 2.2          |                                                            | 17     |  |

|   |              |                                                            | 18     |  |

|   |              | *                                                          | 19     |  |

|   |              | 2.2.3 Multi-Core Execution Model                           | 20     |  |

|   | 2.3          | Principles of Heat Transfer                                | 21     |  |

|   |              | 2.3.1 Thermal Properties of Materials                      | 21     |  |

|   |              | 2.3.2 Heat Transfer Modes                                  | 22     |  |

|   |              | 2.3.3 Current-Thermal Equivalence                          | 24     |  |

| 3 | Ten          | nperature/Power Relationship in Microprocessors            | 25     |  |

| Ŭ | 3.1          |                                                            | 25     |  |

|   | 3.2          |                                                            | 26     |  |

|   | 0            |                                                            | 27     |  |

|   |              |                                                            | 29     |  |

|   |              |                                                            | 31     |  |

|   | 3.3          |                                                            | 31     |  |

|   | 3.4          |                                                            | 33     |  |

|   |              |                                                            | 34     |  |

|   |              |                                                            | 36     |  |

|   |              | 3.4.3 Temperature Transformation Function                  | 37     |  |

|   | 3.5          |                                                            | 39     |  |

|   |              | 1                                                          | 40     |  |

|   |              | 3.5.2 Software                                             | 41     |  |

|   | 3.6          |                                                            | 42     |  |

|   |                     | 3.6.1          | Measurements & Fitting Discussion                    |   | 42              |

|---|---------------------|----------------|------------------------------------------------------|---|-----------------|

|   |                     | 3.6.2          | Parametric Temperature/Power Model                   |   | 47              |

|   | 3.7                 | Tempe          | erature/Power Relationship Application               | • | 50              |

|   | 3.8                 | Conclu         | usion                                                | • | 53              |

| 4 | The                 | En en e        |                                                      |   |                 |

| 4 | <b>1 n</b> €<br>4.1 |                | gy/Frequency Convexity Rule                          |   | <b>55</b><br>55 |

|   | 4.1<br>4.2          |                | of the Art                                           |   | 55<br>58        |

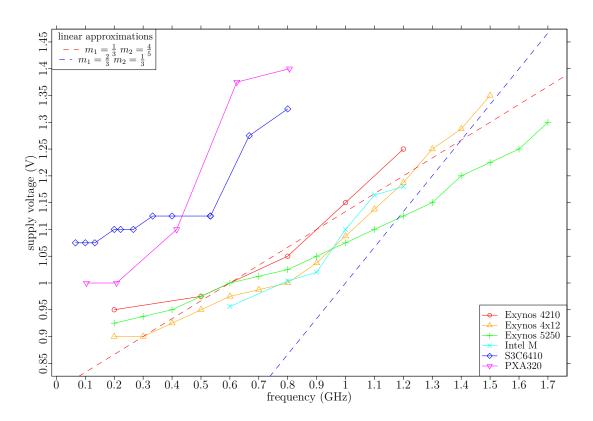

|   | 4.2                 | 4.2.1          | Voltage/Frequency Relationship                       |   | 50<br>59        |

|   |                     | 4.2.1<br>4.2.2 | Energy Consumption Model                             |   | 59<br>60        |

|   |                     | 4.2.2<br>4.2.3 | Approximate Energy Consumption Model                 |   | 60<br>62        |

|   | 4.3                 |                | imental Results                                      |   | 63              |

|   | 4.0                 | 4.3.1          | Platform and Benchmark Description                   |   | 63              |

|   |                     | 4.3.1<br>4.3.2 | Execution Time and Power Measurements                |   | 64              |

|   |                     | 4.3.3          | Energy Consumption                                   |   | 69              |

|   |                     | 4.3.4          | Energy Consumption and Execution Time Relationship   |   | 03<br>71        |

|   | 4.4                 | -              | ivity of the Convexity Model                         |   | 72              |

|   | т.т                 | 4.4.1          | What About Those frequency thieves?                  |   | 72              |

|   |                     | 4.4.2          | Absence of frequency thieves                         |   | $73^{12}$       |

|   |                     | 4.4.3          | Out-of-Order Execution                               |   | 75              |

|   |                     | 4.4.4          | Temperature Dependency                               |   | 76              |

|   | 4.5                 |                |                                                      |   | 77              |

|   | 1.0                 | Conon          |                                                      | • | •••             |

| 5 | Pas                 |                | ooling of Microprocessors                            |   | <b>79</b>       |

|   | 5.1                 | Coolin         | ng in Thermal Management Techniques                  |   | 79              |

|   | 5.2                 | Active         | e cooling: the Newtonian Approach $\ldots$           |   | 81              |

|   | 5.3                 | Passiv         | e Cooling with Internal Heat Generation              |   | 83              |

|   |                     | 5.3.1          | Exact Solution of $f(T) = t$                         |   | 84              |

|   |                     | 5.3.2          | Dimensionless Solution $\chi(\theta) = \tau$         |   | 87              |

|   |                     | 5.3.3          | Applicability of the Exact Heat Equation             |   | 88              |

|   |                     | 5.3.4          | Validation with Finite Element Analysis              |   | 90              |

|   |                     | 5.3.5          | Thermal Runaway                                      |   |                 |

|   |                     | 5.3.6          | Approximate Solutions to $f(t) = T$                  |   |                 |

|   |                     | 5.3.7          | Battle of the Approximate Solutions                  |   |                 |

|   |                     | 5.3.8          | Impulse Responses                                    |   |                 |

|   | 5.4                 |                | e and Active Cooling Law Comparison                  |   |                 |

|   |                     | 5.4.1          | Convective Heat Transfer Coefficient Ratio           |   |                 |

|   |                     | 5.4.2          | Temperature Lag                                      |   |                 |

|   | 5.5                 | Conclu         | usion                                                | • | 109             |

| 6 | Ont                 | imal F         | Energy/Frequency Applications to Multi-Clock Domains | 1 | 111             |

| Ŭ | 6.1                 |                | Buddy Convexity Model                                |   |                 |

|   | 6.2                 |                | Core with Deadlines                                  |   |                 |

|   | <b>.</b>            | 6.2.1          | Modeling Including $P_{idle}$                        |   |                 |

|   |                     | 6.2.2          | Experimental Results                                 |   |                 |

|   | 6.3                 |                | core Code Execution                                  |   |                 |

|   | 6.4                 |                | hl's Law Extension for Energy Efficiency             |   |                 |

|   |                     | 6.4.1          | Extension of Amdahl's Law                            |   |                 |

|   |                     |                | Experimentation                                      |   |                 |

|              | 6.5 | big-LITTLE Heterogeneous Computing                               |

|--------------|-----|------------------------------------------------------------------|

|              | 6.6 | Conclusion                                                       |

| 7            | Con | iclusion 131                                                     |

|              | 7.1 | Final Remarks and Results                                        |

|              | 7.2 | Future Work                                                      |

| $\mathbf{A}$ | Mat | thematical Fundamentals and Derivations 135                      |

|              | A.1 | Derivations                                                      |

|              |     | A.1.1 Deviating Root Configurations                              |

|              |     | A.1.2 Equality of the Second-order O'Sullivan Approximations 136 |

|              | A.2 | Ferarri's Theorem                                                |

|              | A.3 | Statistical Estimator Error                                      |

|              | A.4 | Functions                                                        |

|              |     | A.4.1 Heaviside function                                         |

|              |     | A.4.2 Sign Function                                              |

|              |     | A.4.3 Dirac's Delta function                                     |

| в            | Sou | rce Code Excerpts 141                                            |

|              | B.1 | Implementation of the Passive Cooling Law                        |

|              |     | B.1.1 Exact Solution                                             |

|              |     | B.1.2 Approximations                                             |

|              |     | B.1.3 SPICE simulation                                           |

# List of Figures

| 2.1  | Power breakdown of a computer system                                                                   | 11 |

|------|--------------------------------------------------------------------------------------------------------|----|

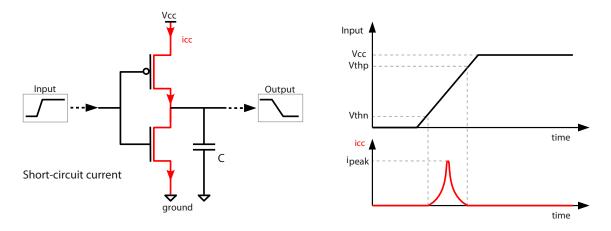

| 2.2  | Inverter exemplifying the switching power                                                              |    |

| 2.3  | Inverter exemplifying the short-circuit power                                                          | 12 |

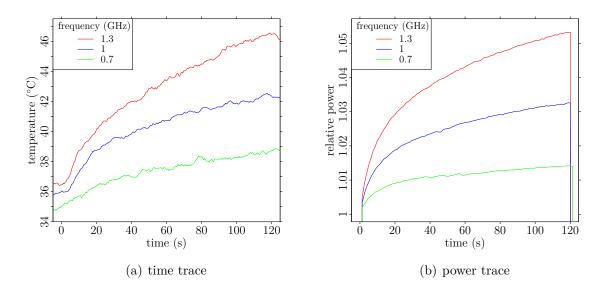

| 2.4  | Microprocessor's temperature and power traces under constant workload $% \mathcal{A}_{\mathrm{res}}$ . | 14 |

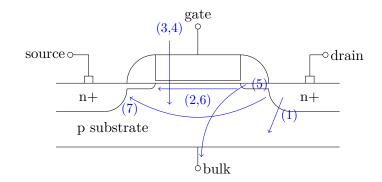

| 3.1  | Schematic NMOS transistor and its leakage currents                                                     | 27 |

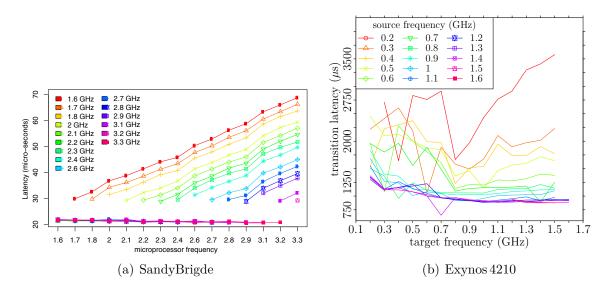

| 3.2  | Microprocessor clock frequency transition latency                                                      | 30 |

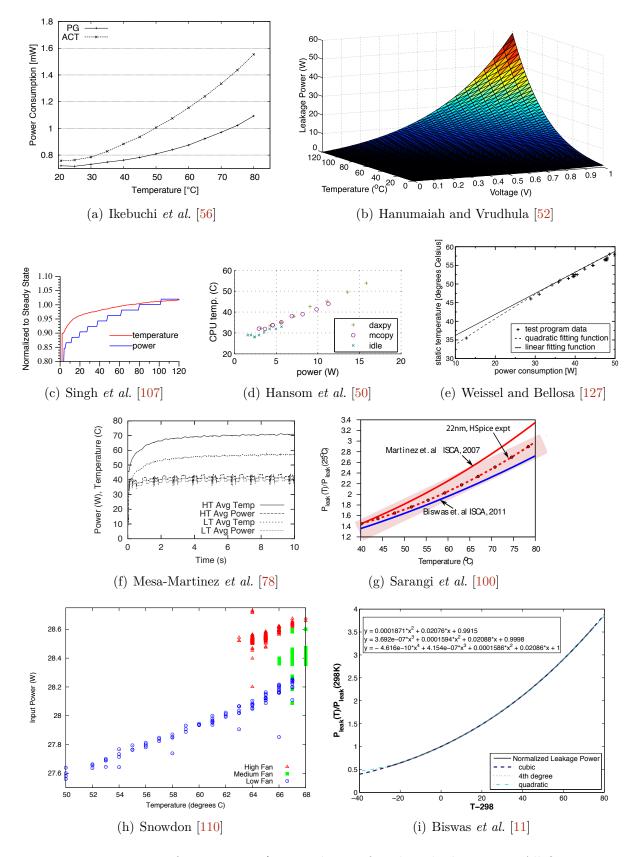

| 3.3  | Excerpts of temperature/power plots                                                                    | 32 |

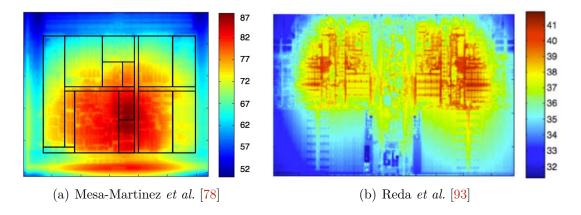

| 3.4  | Examples of thermal images of microprocessors                                                          | 34 |

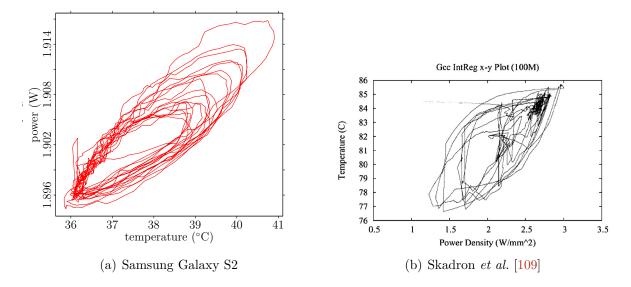

| 3.5  | Temperature/power loops induced by the distant-sensor-syndrome                                         | 35 |

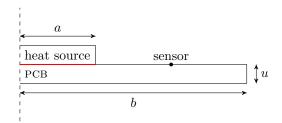

| 3.6  | Axisymmetric model of a sensor and heat source on a disk                                               | 38 |

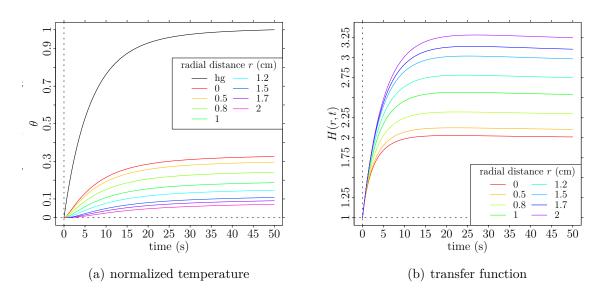

| 3.7  | Transient temperature in a PCB injected with a heat flux                                               | 38 |

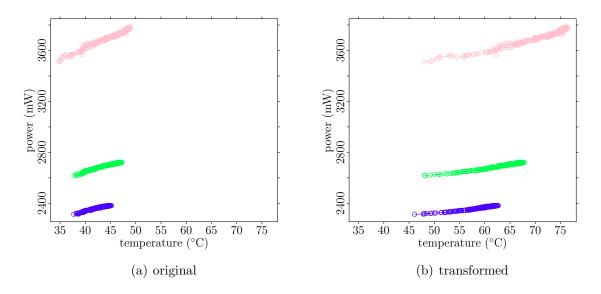

| 3.8  | Transformation of power/temperature traces                                                             | 40 |

| 3.9  | Power measurement devices as used in the testbeds                                                      | 41 |

| 3.10 | Bit-reverse algorithm as per the Gold-Rader implementation                                             | 42 |

| 3.11 | Cortex A7 temperature/power traces                                                                     | 43 |

|      | Cortex A15 temperature/power traces                                                                    | 44 |

| 3.13 | Excerpts of fitted temperature/power traces                                                            | 45 |

|      | Temperature-canceled power/time traces                                                                 |    |

|      | Power distribution of original and transformed power traces                                            |    |

| 4.1  | Excerpts of energy/frequency measurements as found in the literature                                   | 57 |

| 4.2  | Excerpts of energy/frequency measurements (continued)                                                  | 58 |

| 4.3  | Frequency/voltage relationship of multiple microprocessors                                             |    |

| 4.4  | Execution time experimental measurement traces                                                         |    |

| 4.5  | Power consumption measurement traces on the A7, A9 and A15                                             | 67 |

| 4.6  | Power consumption upper and lower bound for the A7 and A15                                             | 69 |

| 4.7  | Experimental energy consumption data for the A7, A9 and A15                                            |    |

| 4.8  | Energy consumption and execution time relationship                                                     |    |

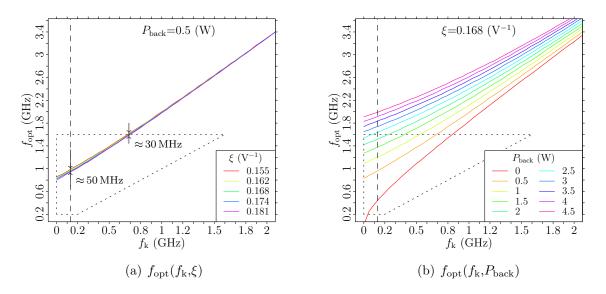

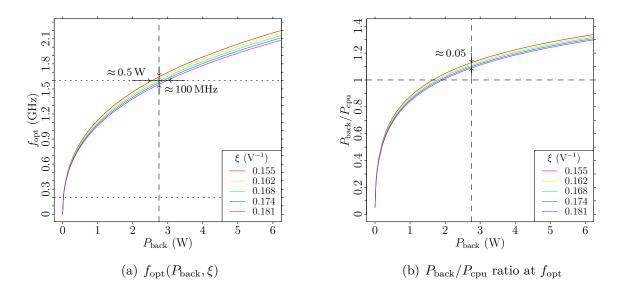

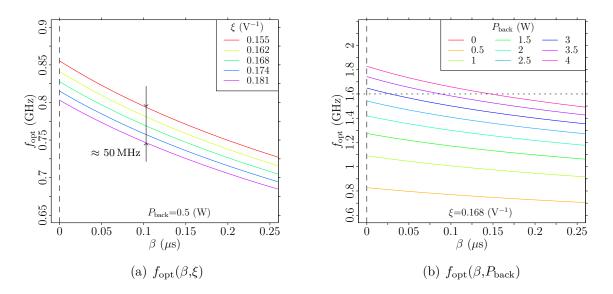

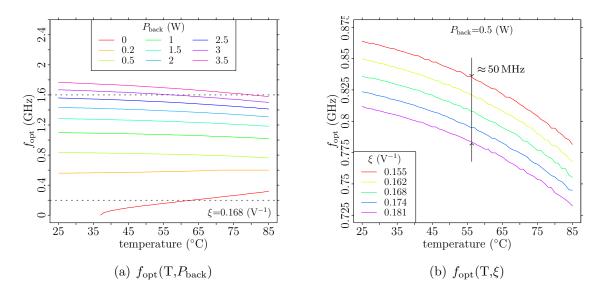

| 4.9  | Optimal frequency for variable level of $f_k$ in function of $\xi$ and $P_{\text{back}}$               |    |

| 4.10 |                                                                                                        |    |

|      | Optimal frequency for variable levels of $\beta$ in function of $\xi$ and $P_{\text{back}}$            |    |

|      | Optimal frequency for floating temperature                                                             |    |

|      | Optimal frequency location w.r.t. the default clock frequency window                                   |    |

| 5.1  | Typical graph of the exact heat equation's dimensionless solution                                      | 88 |

| 5.2  | Visualization of the exact heat equation's differential representation                                 | 89 |

| 5.3  | Validation of the heat equation with CFD                                                               | 91 |

| 5.4  | Thermal runaway explained                                                                              | 93 |

| 5.5  | Realistic scenario of thermal runaway                                                                  |    |

|      |                                                                                                        |    |

| 5.6  | Illustration of the approximate solutions to $f(t) = T$                 |

|------|-------------------------------------------------------------------------|

| 5.7  | RMSE of the exact heat equation's approximations                        |

| 5.8  | Temperature error of the heat equation's approximations                 |

| 5.9  | Heat transfer coefficient ratio between active and passive cooling 106  |

| 5.10 | Relative time lag between active and passive cooling                    |

| 6.1  | Energy state machine representation of a computer component             |

| 6.2  | Frequency time line in a master/slave two-buddy system                  |

| 6.3  | Energy consumption of a recurrent code with a deadline                  |

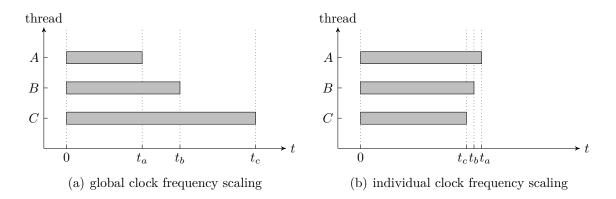

| 6.4  | Energy optimization with individual thread frequency scaling            |

| 6.5  | Energy consumption of multi-thread code execution                       |

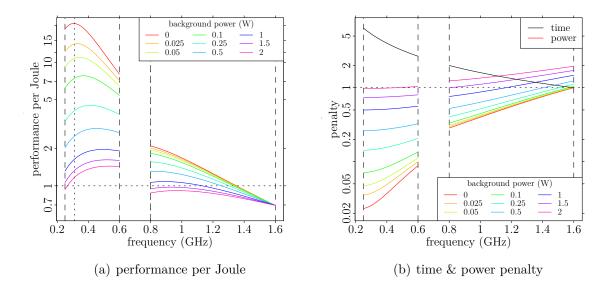

| 6.6  | Performance per Joule; Amdahl's law extension for energy efficiency 124 |

| 6.7  | Big-LITTLE optimal frequency                                            |

| 6.8  | Big-LITTLE performance per Joule                                        |

| B.1  | Illustration of the prototype implementation of $f(T) = t$ in R         |

## List of Tables

| 2.1 | Typical values for the <i>thermal conductivity</i> $(k)$ at room temperature     | 22  |

|-----|----------------------------------------------------------------------------------|-----|

| 2.2 | Typical values for the <i>thermal diffusivity</i> $(\alpha)$ at room temperature | 22  |

| 2.3 | Analogies between heat flow and electrical current transport                     | 24  |

| 3.1 | Leakage current models as found in the literature                                | 29  |

| 3.2 | Power models $P(T)$ considered as for temperature/power modeling                 | 45  |

| 3.3 | Aggregated temperature/power fitting errors for $25^{\circ}C < T < 85^{\circ}C$  | 46  |

| 3.4 | Aggregated temperature/power fitting errors for $25^{\circ}C < T < 55^{\circ}C$  | 46  |

| 3.5 | Practical guidelines for temperature/power model selection                       | 47  |

| 3.6 | Frequency and voltage settings for the A7, A9, and A15 microprocessors .         | 48  |

| 3.7 | Performance of the power transformation                                          | 54  |

| 4.1 | Overview of the Bristol Energy Efficiency Benchmark Suite                        | 64  |

| 4.2 | Benchmarks execution time model parameters                                       | 66  |

| 4.3 | Benchmarks power model parameters                                                | 68  |

| 4.4 | Power consumption coefficients for the upper and lower bounds                    | 69  |

| 5.1 | Parameters assumed for the COMSOL validation simulation                          | 90  |

| 5.2 | Approximations to the exact inverse cooling law $f(t) = T$                       | 100 |

| 5.3 | Parameters assumed for the active and passive cooling laws' simulation           | 105 |

| 6.1 | Amdahl's law scaling factors                                                     | 125 |

## List of Procedures

| 3.1 | Cortex A7 power consumption model                             | 48 |

|-----|---------------------------------------------------------------|----|

| 3.2 | Cortex A15 power consumption model                            | 48 |

| 3.3 | Alternative Cortex A7 power consumption model                 | 49 |

| 3.4 | Alternative Cortex A15 power consumption model                | 49 |

| 3.5 | Cortex A7 exponential temperature/power transformation model  | 50 |

| 3.6 | Cortex A15 exponential temperature/power transformation model | 50 |

# Table of Symbols

| Symbol             | Description                                 | Units             |

|--------------------|---------------------------------------------|-------------------|

| $cc_{\rm b}$       | program clock cycles                        | -                 |

| $f_{\rm k}$        | clock frequency thieves                     | 1/s               |

| $cc_{\rm m}$       | memory clock cycles                         | -                 |

| f                  | clock frequency                             | 1/s               |

| $f_{ m cpu}$       | microprocessor clock frequency              | 1/s               |

| $f_{ m mem}$       | memory clock frequency                      | 1/s               |

| $\sigma_{ m x}$    | out-of-order execution coverage             | -                 |

| С                  | number of active cores                      | -                 |

| $\Delta t$         | execution time / timespan                   | $\mathbf{S}$      |

| $M_a$              | number of external memory accesses          | -                 |

| eta                | average waiting time per clock cycle        | S                 |

| $Q_{\rm sys}$      | heat flux of the system                     | $W/m^2$           |

| $Q_{ m in}$        | heat flux into the system                   | $W/m^2$           |

| $Q_{\rm ihg}$      | heat flux of the internal heat conversion   | $W/m^2$           |

| $Q_{\mathrm{out}}$ | heat flux to the environment                | $W/m^2$           |

| $Q_{ m d}$         | heat flux resulting from conduction         | $W/m^2$           |

| $Q_{ m v}$         | heat flux resulting from convection         | $W/m^2$           |

| $Q_{ m r}$         | heat flux resulting from radiation          | $W/m^2$           |

| m                  | body mass                                   | $\mathrm{kg}$     |

| $c_p$              | specific heat capacity at constant pressure | J/kg·K            |

| ho                 | density                                     | $kg/m^3$          |

| $\alpha$           | thermal diffusivity                         | $m^2/s$           |

| k                  | thermal conductivity                        | W/m·K             |

| A                  | surface area                                | $\mathrm{m}^2$    |

| n                  | normal vector                               | -                 |

| h                  | convective heat transfer coefficient        | $W/m^2 \cdot K$   |

| $h_{ m ac}$        | active cooling heat transfer coefficient    | $W/m^2 \cdot K$   |

| $h_{ m pc}$        | passive cooling heat transfer coefficient   | $W/m^2 \cdot K$   |

| $T_s$              | surface temperature                         | °C or K           |

| $T_a$              | ambient temperature                         | °C or K           |

| $T_0$              | temperature at $t = 0$                      | °C or K           |

| $\sigma$           | Boltzmann constant                          | $W/m^2 \cdot K^4$ |

| $\epsilon$         | emissivity                                  | -                 |

| $\sigma$           | electrical conductivity                     | $\Omega/{ m m}$   |

| r                  | radius                                      | m                 |

| z                  | height                                      | m                 |

| $\varphi$          | angle                                       | с                 |

| $	heta_{ m JB}$    | junction-to-board (thermal) resistance      | $m^2 \cdot K/W$   |

| Symbol           | Description                                          | Units                                         |

|------------------|------------------------------------------------------|-----------------------------------------------|

| $\omega$         | temperature scaling factor                           | -                                             |

| $\omega_*$       | polynomial roots                                     | -                                             |

| $P_r$            | reference power                                      | W                                             |

| $P_m$            | measured power                                       | W                                             |

| ξ                | microprocessor's power profile                       | $W/Hz \cdot V^2$                              |

| $\gamma$         | microprocessor's leakage current profile             | $V^{-1}$                                      |

| $T_r$            | reference temperature                                | $^{\circ}\mathrm{C} \text{ or } \mathrm{K}$   |

| $T_m$            | measured temperature                                 | $^{\circ}\mathrm{C} \text{ or } \mathrm{K}$   |

| $\eta_*$         | fitting parameters                                   | $W/^{\circ}C^{*}$                             |

| $\Delta T$       | temperature difference                               | $^{\circ}\mathrm{C} \mathrm{~or~} \mathrm{K}$ |

| $m_*$            | voltage/frequency regression coefficients            | $V/Hz^*$                                      |

| $s_*$            | power profile regression coefficients                | $W/Hz^*$                                      |

| $s_x$            | power profile scaling factor                         | -                                             |

| $E_{\rm sys}$    | energy consumption of the system                     | J                                             |

| $E_{\mathbf{n}}$ | normalized energy consumption of the system          | J                                             |

| $\eta_*$         | internal heat generation regression coefficients     | $W/K^*$                                       |

| S                | surface area                                         | $m^2$                                         |

| C                | heat capacity of the body                            | J/K                                           |

| $T_{ m tr}$      | point of thermal runaway                             | $^{\circ}\mathrm{C} \mathrm{~or~} \mathrm{K}$ |

| *°               | energy or power in idle-state                        | J or W                                        |

| *+               | energy or power in active-state                      | J or W                                        |

| *                | static energy or power component                     | J or W                                        |

| ~                | dynamic energy or power component                    | J or W                                        |

| $\delta$         | number of energy state transactions                  | -                                             |

| $\varrho$        | proportion of code that is parallelizable            | -                                             |

| n                | number of cores                                      | cores                                         |

| k                | number of active cores                               | cores                                         |

| p                | dimensionless time penalty due to frequency scaling  | -                                             |

| q                | dimensionless power penalty due to frequency scaling | -                                             |

| $\Lambda$        | dimensionless performance scaling factor             | -                                             |

| $\kappa_*$       | polynomial coefficients                              | -                                             |

| $c_0$            | integration constant                                 | -                                             |

|                  |                                                      |                                               |

## Résumé en Français

### Introduction

Même une petite quantité d'énergie économisée grâce à un meilleure contrôle sur la planification de la fréquence et des effets thermiques sur le comportement énergétique des microprocesseurs peut avoir des impacts sociaux, monétaires et écologiques importants. Comprendre et modéliser ces relations avec précision peut avoir un impact au-delà de la seule gestion optimisée de fonctionnement des systèmes informatiques. Cela souligne l'aspect crucial de l'optimisation de l'énergie dans les microprocesseurs, en particulier pour les systèmes embarqués et de calcul haute performance (HPC). Ce point est particulièrement important pour les systèmes utilisant une batterie électrique, tels que les smartphones, capteurs, etc. Quelle que soit leur origine, tous les appareils portatifs partagent en effet le même talon d'Achille: la *batterie* [123]. A l'autre bout du spectre, les systèmes HPC sont eux, entre autres, contraints par l'alimentation électrique disponible.

La disponibilité du service offert par des dispositifs alimentés par batteries est une question critique pour quasiment tout utilisateur ou exploitant. L'autonomie de la batterie est devenue un facteur important pour l'expérience utilisateur, comme cela a été démontré par des études académiques [37] ainsi que par des enquêtes menées par les canaux d'information de détail <sup>1</sup> depuis la création des appareils portables. Même si la capacité des batteries et leurs performances augmentent au fil du temps, l'amélioration de l'efficacité énergétique des systèmes à base de batterie est et reste essentielle, parce que entre autres, la demande de puissance devance les développements dans les capacités des batteries [94, 117]. Les super-ordinateurs, d'autre part, sont eux limités par la puissance disponible fournie par le réseau alimentant le centre de données. Ces ordinateurs doivent donc fonctionner avec une puissance et un budget contraints. En outre, l'expérience utilisateur, les produits et la conception de circuits sont limités par la dissipation en puissance de crête des composants électriques. Comprendre les différents aspects de la consommation de l'énergie des systèmes (embarqués) est donc une question clé. La fréquence du processeur, ainsi que la durée et la température de l'exécution, sont, entre autres, des facteurs importants qui influencent la consommation d'énergie et le profil de puissance de l'exécution des programmes lié à l'architecture hardware sur laquelle il s'exécute. Fournir des modèles de consommation d'énergie peut ainsi ouvrir la voie à l'optimisation de l'énergie à l'interface entre logiciel et matériel.

Historiquement, les performances en termes de temps d'exécution ou de consomation mémoire ont été la principale mesure de la performance au niveau des couches logicielles et matérielles. Aujourd'hui, l'efficacité énergétique et la dissipation d'énergie deviennent des indicateurs de performance tout autant importants, surtout pour les appareils alimentés

<sup>&</sup>lt;sup>1</sup>Autonomie : préoccupations des utilisateurs mobiles: http://www.cnn.com/2005/TECH/ptech/09/ 22/telephone

par des batteries. Le temps d'exécution demeure bien sûr une mesure de performance pour les systèmes qui nécessitent une performance soutenue, comme les super-ordinateurs. Mais pour les systèmes qui sont conçus pour offrir une interface homme-machine riche, la puissance de calcul soutenue n'est pas nécessairement un objectif primordial ; en revanche, les temps de réponse de l'application doivent suffire à satisfaire l'expérience de l'utilisateur. Ces approches différenciées de l'informatique peuvent nécessiter des méthodes d'optimisation de l'énergie différentes. Par exemple, des bouffées sporadiques de dissipation de puissance dépassant l'enveloppe thermique (TDP) (Thermal Design Power) peuvent être inoffensives pour le matériel et offrir un soutien temporaire pour un système devant être prêt â répondre rapidement [90].

Optimiser de manière efficace le profil de puissance du microprocesseur et le flux de chaleur qu'il génère est une question cruciale pour les technologies futures. Les technologies actuelles et futures ne peuvent permettre, dans les cas les plus extrêmes, qu'à un sous-ensemble de la logique du microprocesseur d'être actif à un moment donné pour rester compatible avec les niveaux acceptables de dissipation de puissance maximale du microprocesseur. La fraction de logique ainsi désactivée est appelée *silicium noir*. En outre, les limites de puissance et de temps de transmission physique ont conduit à maintenir constante la fréquence d'horloge des technologies actuelles et futures [33]. En conséquence, pour améliorer la performance, le parallélisme est aujourd'hui de plus en plus employé dans les microprocesseurs. Le multi-threading simultané (SMT) sur multi-coeurs a fourni des économies d'énergie substantielles avec le matériel récent [34].

Outre l'optimisation de l'efficacité énergétique au niveau matériel, le logiciel peut également être conçu de façon à minimiser les exigences de consommation d'énergie. Pour les systèmes embarqués, six aspects d'optimisation de l'énergie peuvent se trouver au niveau logiciel: les systèmes d'exploitation orientés-énergie, la gestion efficace des ressources, l'impact de la configuration de l'interaction des utilisateurs avec les appareils mobiles et les applications, les interfaces sans fil, la gestion des capteurs et la prise en compte des services informatiques de Cloud [117]. Toutes ces facettes pourraient être optimisées individuellement, mais elles doivent plutôt être optimisées de concert pour atteindre le plus grand gain d'énergie. Il s'agit là d'une tâche ambitieuse et complexe. Au niveau logiciel, les techniques d'optimisation d'énergie et de puissance peuvent être grossièrement divisées en méthodes statique et dynamique. Les méthodes statiques comprennent, entre autres, la conception efficace de logiciels et l'optimisation du compilateur. Pour que ces approches permettent d'optimiser énergie et puissance, un profil énergétique du matériel sur lequel l'exécution du logiciel est prévue est nécessaire. Cela comporte l'inconvénient que le logiciel ne sera optimal, pour une valeur d'énergie ou de puissance donnée, que pour un type de configuration matérielle spécifique. Avec ce type d'optimisation statistique, cependant, la spécification du matériel peut ne pas être connue complètement et des informations de contexte peuvent ne pas toujours être disponibles, par exemple, lors de l'étape de développement. En outre, la conception de l'architecture économe en énergie est très sensible à la charge, nécessairement variable, de travail [34] du processeur. Cela impose une incertitude sur l'efficacité finale des techniques d'optimisation statiques.

L'optimisation dynamique, d'autre part, présente l'avantage que des informations de contexte sont disponibles et les spécifications du matériel sont connues. Avec ces informations supplémentaires, si elle sont accessibles, le système et le logiciel peuvent dynamiquement s'adapter pour améliorer l'efficacité énergétique et de puissance. Parmi les méthodes en ligne, on trouve : l'optimisation dynamique de compilation, l'optimisation du bytecode, et les techniques d'optimisation au niveau du système. Comme pour l'optimisation statique, la connaissance des profils énergétiques du matériel et des logiciels contribue à améliorer les décisions prises par les techniques dynamiques d'optimisation d'énergie et de puissance.

L'objectif de cette thèse est de se concentrer sur les profils énergétiques et, plus précisément, sur la façon dont deux paramètres fondamantaux : la température et la fréquence d'horloge du microprocesseur affectent la consommation d'énergie et les conditions de fonctionnement optimales d'un système informatique.

#### La loi de convexité énergie – fréquence

Les courants circulant dans un microprocesseur, ou circuit intégré (IC), respectent les lois fondamentales d'électricité (Ohm, Kirchhoff, ...). Ainsi ils produisent une dissipation de chaleur proportionnelle à  $I^2R$ , où R est la résistance et I le courant électrique global du système étudié. La première loi de la thermodynamique indique que, en fonctionnement régulier, l'apport d'énergie d'un système est égal à la consommation d'énergie du système. Ainsi, en l'absence d'autres interactions de l'énergie, et en négligeant l'information liée à l'énergie elle-même, la seule forme d'énergie émanant d'un microprocesseur est la chaleur engendrée par les courants circulant à travers des éléments résistifs [17]. Par conséquent, la dissipation de chaleur du microprocesseur est très proche de sa consommation d'énergie. Le processus de génération de chaleur interne du microprocesseur est parfois aussi appelé conversion de chaleur interne. Un microprocesseur présente un comportement thermique transitoire où les délais de refroidissement et de chauffage dépendent de sa capacité calorique. Le comportement thermique transitoire dure plus longtemps pour les systèmes ayant des capacités caloriques plus grandes que pour ceux ayant des capacités plus petites. Ces systèmes sont traditionnellement modélisés par des circuits RC, en se fondant sur l'équivalence courant/chaleur (voir la section 2.3.3), à savoir un filtre passe-bas, où la température du système est proportionnelle à la tension aux bornes des condensateurs [27].

En réalité, le comportement (transitoire) thermique est plus compliqué, parce que la résistance R et les courants I dépendent de la température du microprocesseur. D'une manière générale, il est démontré expérimentalement que le besoin de puissance croît super-linéairement avec la température du système. Dans le chapitre 3, cette relation entre température et puissance est analysée en détail. En particulier, les comportements thermiques de trois processeurs d'applications pour systèmes embarqués sont discutés. Il sera montré que la relation température / puissance est correctement modelisée par une loi exponentielle. Pour de petites variations de température, que l'on rencontre fréquemment dans les systèmes embarqués, des approximations linéaires et quadratiques sont adéquates. En outre, des modèles de transformation de puissance sont conçus afin de servir à éliminer les biais de température à partir de traces de mesure, et de réduire ainsi les effets de distance et de dispersion d'un capteur de température lointain. De tels modèles d'alimentation et de transformation sont intéressants pour les raisons suivantes.

- Les mesures sont essentielles pour la compréhension puis l'optimisation des systèmes énergie critique [34, 117]. Un manque de mesures de puissance détaillées portera atteinte aux efforts visant à réduire la consommation d'énergie sur un logiciel moderne [34].

- Des travaux de recherche ont essayé de décrire la relation température / puissance en se concentrant sur un sous-ensemble des courants de fuite décrits par BSIM [36, 68, 69, 108, 114]. De tels modèles font l'hypothèse que les courants de fuite sont

uniquement dépendants de la température. Les courants, cependant, sont également fonction du temps, car les tensions appliquées aux bornes des transistors changent avec le temps, ce qui introduit une complexité supplémentaire de modélisation. Les courants de fuite dépendent d'une multitude de facteurs spécifiques à chaque microprocesseur, qui ne sont pas tous encore connus précisément. Par conséquent, il peut être intéressant de proposer une modélisation agrégée de la relation température / puissance, comme approche alternative aux modèles dérivés de BSIM.

- En outre, il est essentiel de bien comprendre l'importance des erreurs dues aux mesures de puissance en fonction des différents régimes de température du système à l'étude. Par exemple, certaines de nos mesures de puissance exhibent jusqu'à 10% d'écart en raison d'effets transitoires de température [28]. Ainsi, si les mesures de puissance doivent être comparées, il est interessant que les effets de la température puissent être controlés de manière à obtenir une base équitable d'analyse.

- Du point de vue de la mesure, il est également important de comprendre l'impact de la génération de chaleur interne sur la température et de l'effet de capteurs distants. Des protocoles de mesures de puissance précis et reproductibles sont difficiles à établir, en raison du comportement thermique transitoire des composants électriques. Plus précisément, pour un programme de test donné, la mesure de l'alimentation du microprocesseur peut conduire à des valeurs différentes pour différentes températures du microprocesseur. Par souci de précision et de comparaison équitable entre différentes mesures de puissance, il est donc d'une importance vitale de pouvoir contrôler ou annuler les effets du comportement thermique transitoire.

La dépendance en température fait partie des spécifications relatives à un microprocesseur; des températures élevées ont un effet négatif sur sa durée de vie. La fiabilité des produits électroniques est influencée par les gradients spatiaux ou temporels de température, ainsi que par leurs valeurs, dans l'absolu [63]. Les gradients thermiques, qui se produisent à la fois dans l'espace et dans le temps, induits par la variabilité de la charge de microprocesseur et des opérations, engendrant des cycles thermiques qui ont un effet négatif sur le taux de panne des systèmes [60]. L'International Technology Roadmap for Semiconductors (ITRS) affirme même que les coûts de traitement et les spécifications de performance peuvent être limités par la durée de vie, la fiabilité étant la principale préoccupation dans la phase de conception d'un microprocesseur [51]. Le temps moyen avant fin de bon fonctionnement (MTTF) des équipements électroniques diminue de façon exponentielle avec la température ; les causes possibles de panne sont l'électromigration, les réactions chimiques, la rupture diélectrique, ou le fluage dans les matériaux de collage [17]. Une augmentation de la température de 10° C à 15°C peut réduire de moitié la vie d'un microprocesseur [125]. Par conséquent, la température d'un système est souvent limitée pour contrôler la dissipation de la chaleur au maximum de puissance, augmenter le MTTF, minimiser la consommation d'énergie, éviter l'autodestruction, ainsi que pour des raisons de sécurité. Les smartphones sont souvent plafonnés thermiquement autour de 50°C, de sorte que les utilisateurs ne se brûlent pas, mais aussi afin d'utiliser efficacement la capacité électrique de la batterie. Soulignons que la température de la surface au contact des systèmes électroniques devrait être limitée à 41°C ou 45°C, en fonction du matériau, afin d'assurer le confort tactile de l'utilisateur [9].

Les équipements électroniques avancés emploient des techniques de gestion de la température (Thermal Management Units (TMUs) ou Dynamic Thermal Management

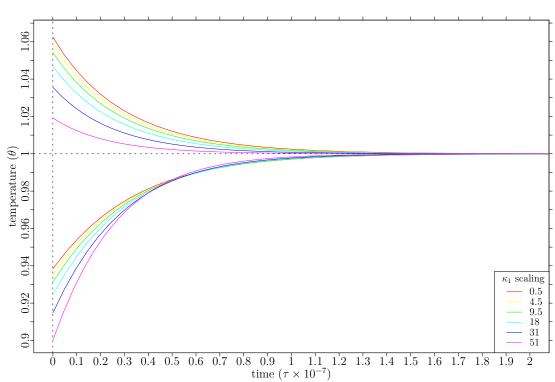

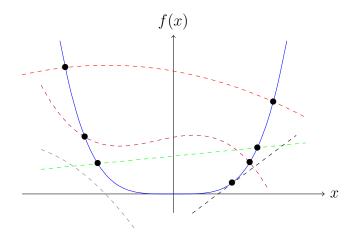

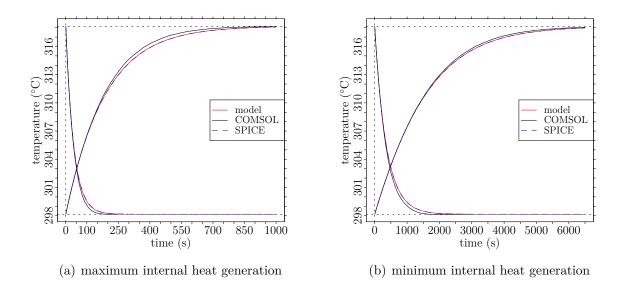

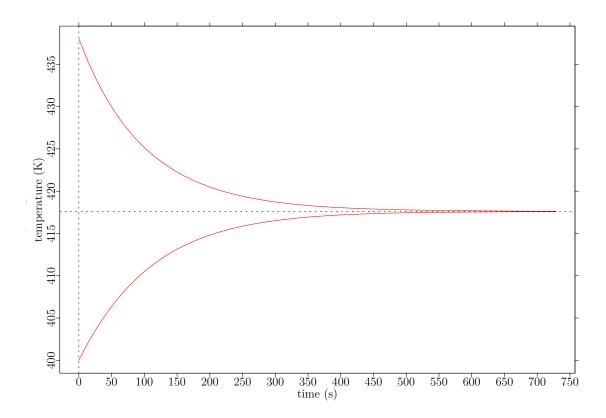

(DTM)) qui sont capables de ralentir ou adapter les systèmes de façon à ce que leurs contraintes thermiques, parfois strictes, soient remplies. Ces techniques de gestion thermique peuvent être mises en place dès la phase de conception du système ou être dynamiquement déployées au moment de l'exécution. Une pléthore de méthodes de contrôle thermique pour microprocesseurs et systèmes sur une puce (SoC) [8, 60] existent ; elles agissent sur les compromis entre profil de température, paramètres de fréquence, consommation d'énergie et complexité de mise en œuvre [138]. Certains microprocesseurs complexes peuvent employer des TMUs implantées sur le matériel, comme, par exemple, certains microprocesseurs d'Intel [31, 77], tandis que les TMUs logicielles sont fréquemment mises en œuvre dans les systèmes embarqués. Pour utiliser efficacement les TMUs, il est important de comprendre le comportement thermique transitoire du système. Le comportement thermique transitoire d'un système refroidi de manière active peut être fidèlement décrit par une relation exponentielle. Mais, pour les systèmes refroidis passivement, tels que les smartphones, les capteurs sans fil ou encore de nombreux objets participant à l'Internet des objets (IoT), l'hypothèse exponentielle ne tient pas. Les systèmes à refroidissement passif comptent sur le refroidissement par conduction, convection naturelle, et rayonnement et sur la gestion thermique de la TMU ou DTM, qui présentent des propriétés non-linéaires. Dans le chapitre 5, le comportement thermique d'un microprocesseur refroidi passivement est étudié par l'intermédiaire du développement d'une loi de refroidissement passif utilisant la conversion de chaleur interne et les mécanismes de refroidissement convectif et radiatif. Des solutions approchées sont également présentées, car la solution exacte est assez complexe et donne le temps t en fonction de la température T alors qu'il serait naturel d'avoir l'inverse, c'est à dire la temperature en fonction du temps. La performance des solutions approchées est aussi évaluée. L'approximation des coefficients se révèle une bonne solution heuristique dans la majorité des cas, avec un minimum d'erreurs en présence de variations de température d'applications embarquées typiques. Pour un objet comme un microprocesseur, il est montré que, pour les grandes surfaces de refroidissement, la loi de refroidissement passive diffère sensiblement d'une loi exponentielle de refroidissement. Pour les surfaces de refroidissement plus petites qu'environ  $1 \,\mathrm{dm}^2$ , la loi de refroidissement passive reste proche d'une loi exponentielle. Pour de tels systèmes, une loi exponentielle de refroidissement, même moins précise, reste avantageuse en termes de mise en œuvre et de complexité de calcul.

En plus de la température, d'autres paramètres influencent le profil de la consommation d'énergie d'un microprocesseur. Les caractéristiques de temps d'exécution et les exigences de puissance du logiciel et du système sont les principaux facteurs qui définissent la consommation finale d'énergie. Ceci est une conséquence directe de la définition de la consommation d'énergie électrique : l'intégrale de la puissance électrique au fil du temps. Le temps d'exécution est influencé par le type et le coût des opérations effectuées par le logiciel en question, y compris les instructions accédant à la mémoire externe et aux registres. Chaque unité fonctionnelle au sein d'un microprocesseur et composant du système a son propre profil de puissance et de temps d'exécution. En conséquence, chaque logiciel a des exigences différentes de puissance. Par exemple, Carroll et Heiser [16] ont montré que, pour leur système embarqué, en exécutant eQuake, vpr, et gzip de SPEC CPU2000, la consommation d'énergie du microprocesseur dépasse la consommation due à la seule mémoire RAM, tandis que c'est l'inverse pour crafty et mcf, issus de la même suite logicielle. Minimiser le nombre d'opérations d'accès à la mémoire est une technique d'optimisation énergétique courante. Par exemple, Intel a introduit, avec la puce E5 Xeon Data Direct I/O (DDIO), le carte réseau (NIC) Ethernet peut charger des données

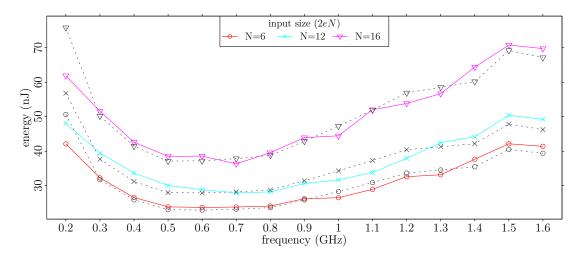

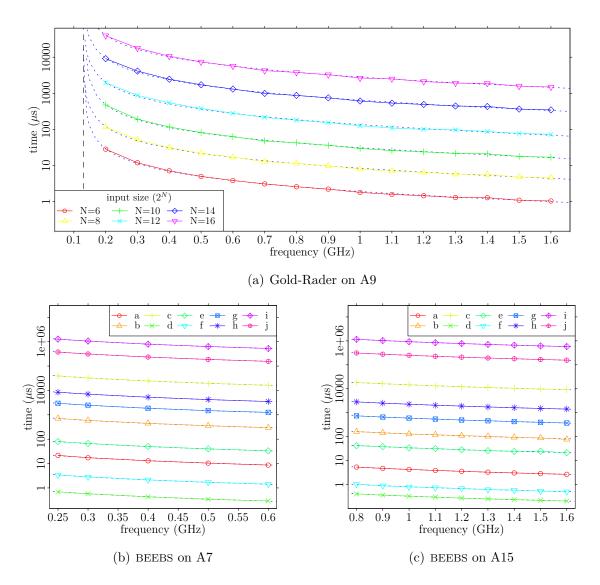

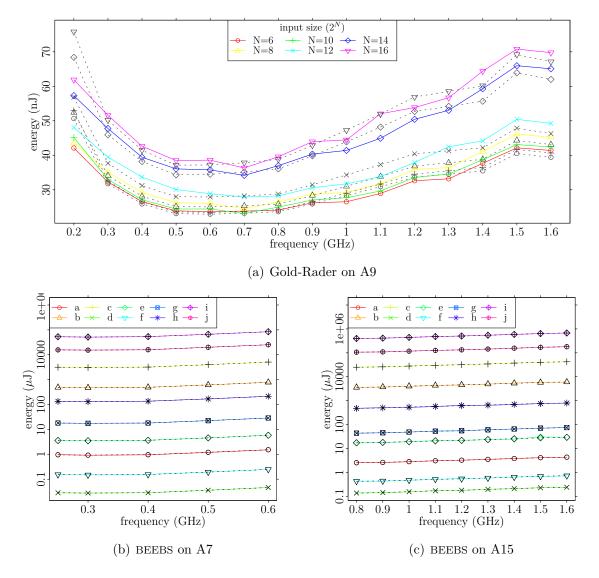

**Figure 1:** Données expérimentales et théoriques de consommation d'énergie d'un programme s'executant sur les microprocesseurs ARM Cortex A9. La consommation d'énergie pour divers points caractéristiques avec différentes tailles des entrées est représentée pour l'algorithme Rader, ainsi que les repères BEEBS. Les traits pleins représentent les données mesurées, tandis que les lignes en pointillé représentent la courbe d'énergie et de temps d'exécution calculée.

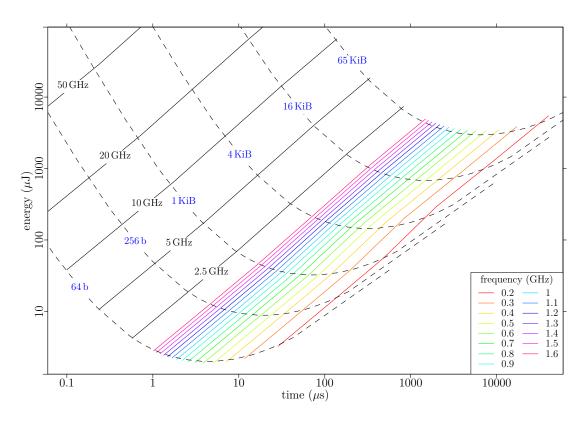

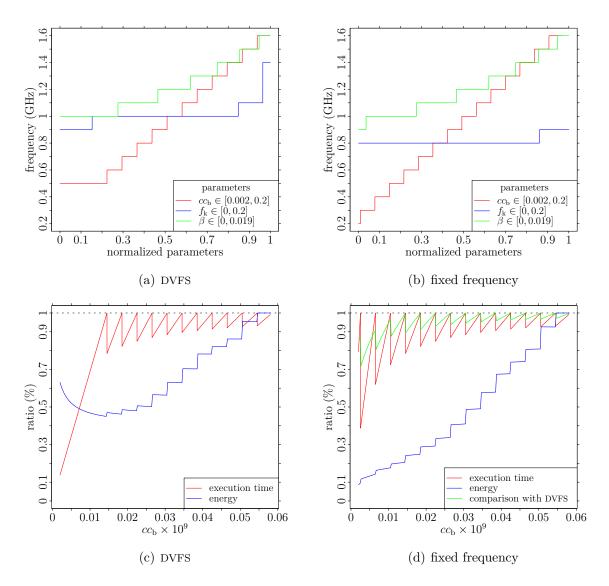

directement dans le cache du microprocesseur [57], minimisant ainsi l'accès a la mémoire mémoire vive (RAM). En évitant les opérations d'entrées-sorties (I/O), la performance, mais aussi la consommation d'énergie du système, est améliorée. Une caractéristique intéressante de la consommation d'énergie d'une séquence de code, c'est que le produit de son temps d'exécution et de la consommation d'énergie du microprocesseur possède, sous certaines hypothèses, des propriétés convexes, ce qui est discuté dans le chapitre 4; cette loi est appelée loi de convexité énergie-fréquence de la consommation des programmes: elle est illustrée dans la figure 1. Cette règle stipule qu'il existe une fréquence d'horloge pour l'exécution de chaque séquence de code qui minimise la consommation d'énergie de ladite séquence de code. Dans certaines conditions, cette fréquence d'horloge optimale, qui réduit la consommation d'énergie, se trouve entre les fréquences d'horloge minimale et maximale de fonctionne du microprocesseur. Comme on le verra, le choix de la fréquence d'horloge optimale conduit à un compromis entre performance en termes de temps d'exécution et économies d'énergie. Pour les applications nécessitant de nombreuses interactions humaines, il a été montré que la fréquence d'horloge peut être réduite sans affecter considérablement l'expérience de l'utilisateur [101]. Une preuve expérimentale de l'existence de la loi de convexité énergie-fréquence de la consommation des programmes, qui concerne la consommation d'énergie et la fréquence d'horloge des microprocesseurs sur les appareils mobiles, est présentée. La propriété de convexité semble garantir l'existence d'une fréquence optimale où la consommation d'énergie est minimale. Cette affirmation de l'existence d'une telle propriété est fondée sur des preuves à la fois théoriques et pratiques. Les données recueillies par l'intermédiaire de campagnes d'acquisition de donnée sur plusieurs plates-formes suggèrent que l'énergie consommée par élément d'entrée est fortement corrélée avec la fréquence d'horloge du microprocesseur et, ce qui est encore plus intéressant, que la courbe correspondante présente un minimum clair sur une fenêtre de fréquences spécifique au système informatique et au programme. Un modèle analytique de ce comportement est aussi motivé, qui cadre bien avec les données présentées. Une analyse de sensibilité des paramètres est réalisée afin d'évaluer l'influence des paramètres sur la

fréquence optimale. Il est également montré que la fréquence optimale augmente lorsque les besoins en puissance du système, à l'exclusion des microprocesseurs, augmentent. La présence de cycles d'horloge perdus pour la gestion propre du système accroît également la fréquence optimale. La fréquence optimale telle que dérivée du cadre théorique présenté ici est cependant indépendante du nombre d'instructions à exécuter.

Dans le chapitre 6, la loi de convexité énergie-fréquence de la consommation des programmes, comme le montre bien la Figure 1, est utilisée dans des applications pratiques. On montre comment on peut calculer les fréquences optimales minimisant la consommation d'énergie du système pour des systèmes intégrant plusieurs entités ayant chacune leur propre fréquence d'horloge, ce qui correspond, en substance, à une superposition de plusieurs systèmes unitaires. La loi de convexité énergie-fréquence de la consommation des programmes est également appliquée à un système informatique soumis à des contraintes temporelles répétitives et à l'adaptation de la fréquence d'un système multithread. Il est ainsi montré que des économies d'énergie de l'ordre de 30 % sont réalisables dans ces cas. Dans le prolongement de la loi d'Amdahl, on analyse le rendement d'énergie d'un système informatique hétérogène. Cette mesure de performance met en lumière les avantages des systèmes à haute performance ne nécessitant qu'une faible puissance.

### Contributions

Ce travail fournit une meilleure compréhension à la fois théorique et pratique de la consommation d'énergie d'un microprocesseur. L'analyse du comportement thermique transitoire et les gains d'énergie via l'adaptation de la fréquence d'horloge sont d'un intérêt tout particulier. Les principales contributions sont :

- un cadre théorique pour la loi de convexité énergie-fréquence de la consommation des programmes et des mesures expérimentales – une analyse de sensibilité de la loi de convexité énergie-fréquence de la consommation des programmes est effectuée pour estimer l'impact des multiples paramètres;

- une loi de refroidissement exacte pour un objet isotherme soumis au rayonnement, à la convection, et à la génération de chaleur interne – la loi exacte est appliquée à un objet de type microprocesseur en vue d'évaluer son comportement transitoire;

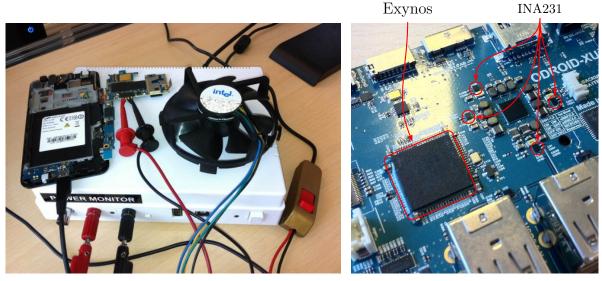

- des modèles température / puissance appliqués à l'Exynos 5410 ces modèles sont utiles pour annuler le biais de température dans les mesures de puissance et d'augmenter la précision de celles-ci;

- des modèles de puissance explicites pour l'Exynos 5410 système sur une puce (SoC) intégrant la fréquence d'horloge, la température, et le nombre de cœurs actifs ces modèles peuvent être directement réutilisés dans toute simulation pour d'autres processeurs d'architecture similaire;

- plusieurs approximations à la loi de refroidissement exacte ces approximations sont plus simples et plus convenablement formulées pour une utilisation pratique;

- des méthodes et lignes directrices concrètes pour améliorer la précision et la pertinence des mesures d'énergie et de puissance;

- des règles générales pour évaluer quand le refroidissement passif devient non négligeable par rapport à un refroidissement actif dans les systèmes embarqués;

• et la mise en œuvre sous forme de prototypes de tous ces modèles de refroidissement – les lois exactes et approximatives pour les objets refroidis passivement sont fournies avec une évaluation de la precision perdues pour les approximations qui d'autres part, permetent un calcul rapide (utilisable dans des applications temps réel).

### Résumé des chapitres

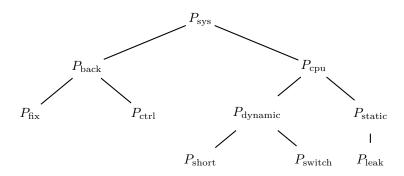

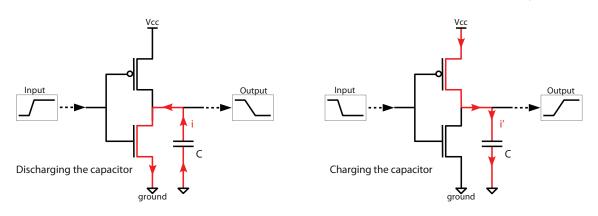

### Généralités sur la consommation d'énergie électrique et le transfert de chaleur

Les concepts fondamentaux sur la consommation d'énergie électrique et le transfert de chaleur sont rappelés dans ce chapitre. Pour comprendre et modeliser la consommation d'énergie électrique, les différentes sources de consommation d'énergie lors de l'exécution d'un programme sont prises en compte. Les modèles de temps d'exécution sont également nécessaires. Au total, ces modèles permettront d'étudier la consommation d'énergie des différents types d'applications dans les chapitres suivants. La température joue un rôle majeur dans la consommation d'énergie lors de l'exécution d'un programme. De ce fait, des modèles de transfert de chaleur sont étudiés ; ils seront utilisés pour comprendre le comportement thermique transitoire d'un microprocesseur.

La section 2.1 présente les notions de consommation d'énergie électrique et de profil de puissance dans le cadre des systèmes informatiques. Les différentes sources de consommation d'énergie dans un microprocesseur sont mises en évidence. Dans la section 2.2, des modèles de temps d'exécution d'un programme sont utilisés conjointent au modèles énergétiques . Des modèles thermiques seront utilisés pour comprendre l'interaction entre l'énergie et la température ; donc la section 2.3 présente un résumé des principes thermiques, y compris les modes de transfert de chaleur et les propriétés thermiques des matériaux.

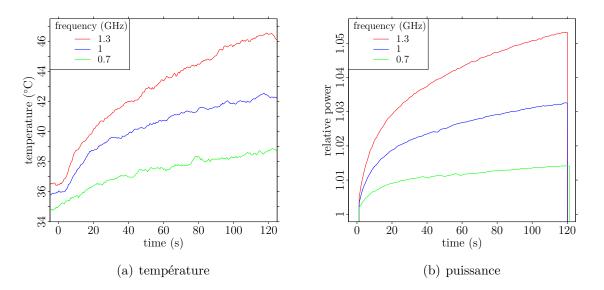

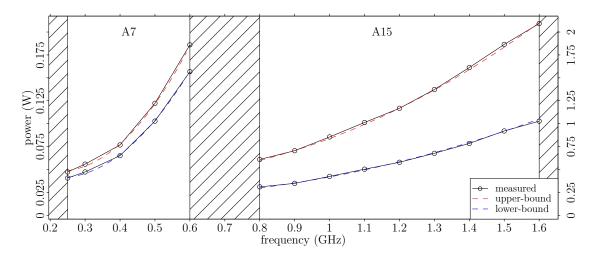

### La relation de température / puissance dans les microprocesseurs

Lorsqu'on étudie la consommation d'énergie sur la base de mesures de puissance, il est impératif d'obtenir des échantillons de puissance précis et des traces de mesures reproductibles. En effet, la température a un impact clair sur les mesures de puissance des microprocesseurs. L'exemple de la figure 2 montre une augmentation de la consommation d'énergie de 5% pour une augmentation de température de 10°C. Auparavant, il avait été également souligné que les courants de fuite sont dépendants de la température, et une équation avait été introduite pour en fournir une approximation. Par conséquent, la puissance d'un microprocesseur est également dépendante de la température et la consommation d'énergie du microprocesseur en est affectée.

La relation entre la consommation d'énergie et la température est ici démystifiée. Les modèles décrits dans la littérature sont remis en question et des traces de mesures expérimentales sont utilisées pour valider certains de ces modèles. L'utilisation pratique des modèles de température / puissance est illustrée avec le but d'améliorer la précision des mesures. L'importance de l'emplacement de la sonde de température par rapport aux sources de chaleur est mise en évidence quantitativement. Un autre modèle de transformation est avancé, qui prend en compte l'emplacement et le comportement des capteurs de température. Quand un capteur de température est placé à distance à partir d'une source de chaleur, le capteur mesure la température avec un retard et avec une amplitude

**Figure 2:** Température (a) et puissance (b) d'un Exynos 4210 en vertue de la charge de travail constante, opérationnel à différentes fréquences d'horloge microprocesseur. On observe que la consommation d'énergie augmente rapidement due à l'augmentation de la température croissante du microprocesseur, étant donné que tous les autres paramètres ont été maintenus constants [28].

diminuée. Ce chapitre traite ainsi de la transformation des traces de puissance, en mettant l'accent sur la température du système, pour arriver à des échantillons de puissance significatifs et reproductibles.

# La loi de convexité énergie-fréquence de la consommation des programmes

Dans le chapitre 2, des modèles de puissance et de temps d'exécution ont été présentés, lesquels, quand ils sont combinés, produisent un modèle de consommation d'énergie du microprocesseur, selon équation 2.2. Dans ce chapitre, le comportement de ce modèle de consommation d'énergie est étudié via une analyse de sensibilité en fonction d'une selection de parametres et sa validité est montrée en pratique grâce à des mesures expérimentales de temps d'exécution et de puissance.

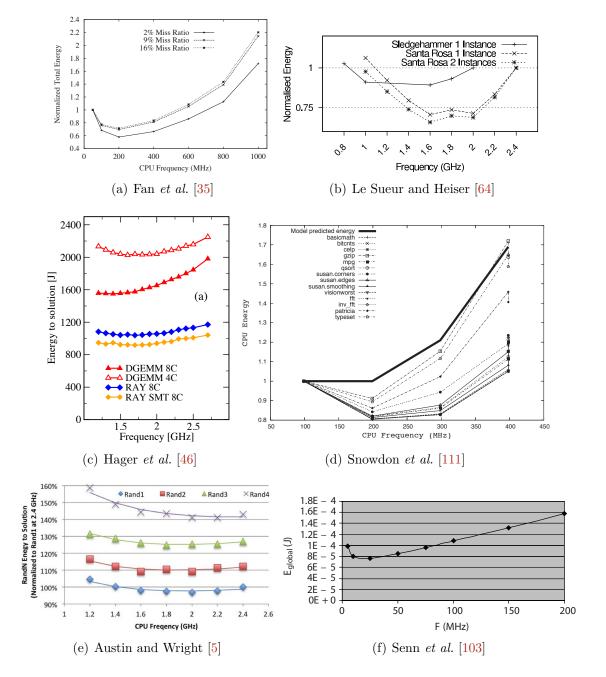

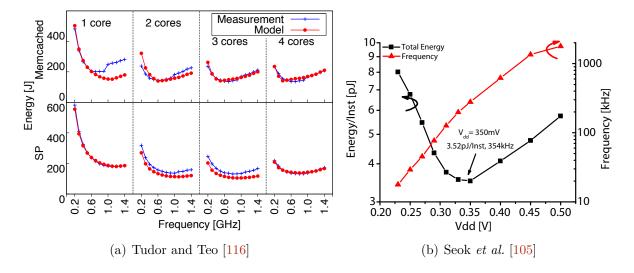

Le chapitre commence par un large état de l'art présentant des courbes d'énergie / fréquence trouvées dans la littérature. La loi de convexité énergie-fréquence de la consommation des programmes pour un microprocesseur à cœur unique est développée dans la section 4.2. Ensuite, dans la section 4,3, des mesures expérimentales de la puissance et du temps d'exécution de deux processeurs sont présentées ; elles montrent l'existence de la convexité énergie / fréquence. Ces modèles fondés sur des campagnes de mesures seront également utilisés dans les chapitres suivants. La section 4.4 analyse, quant à elle, la sensibilité des paramètres de la loi de convexité énergie-fréquence de la consommation des programmes.

#### Le refroidissement passif des microprocesseurs

Une solution analytique exacte du transfert de chaleur au sein d'un microprocesseur refroidi passivement est développée dans ce chapitre, sous les hypothèses de présence de convection, rayonnement et génération de chaleur interne. Ces modèles seront utiles aux Thermal Management Units (TMUs) et Dynamic Thermal Management (DTM) pour évaluer et prédire le comportement thermique d'un microprocesseur. Alors qu'on a auparavant étudié la dépendance de la température sur la puissance du microprocesseur, on se penche ici sur le comportement thermique transitoire. Analyser le comportement thermique exact d'un microprocesseur est intractable en raison de la nature complexe de la physique impliquée dans un circuit intégré y compris la dynamique des fluides, tous les modes de transfert de chaleur, les configurations des composants électroniques complexes, la turbulence, etc. Pour maitriser cette complexité, des hypothèses de simplification sont formulées, par example, ou représente un microprocesseur, par une pièce isotherme d'oxyde de silice qui est placée dans un espace ouvert infini soumis à la convection (naturelle) et au rayonnement. Ces hypothèses sont formulées supposées lorsqu'il s'agit de prendre en compte la loi de refroidissement de Newton.

Tout d'abord, dans la section 5.2, le comportement temporel de la température d'un microprocesseur est considéré, en partant de la loi générale de refroidissement de Newton et la génération de chaleur interne. Ensuite, dans la section 5.3, l'impact de la radiation enrichit notre modèle, pour développer une équation de chaleur modélisant le refroidissement passif d'un microprocesseur avec une génération de chaleur interne. La différence de performance entre les lois de refroidissement passif et actif est également évaluée dans la section 5.4. Par ailleurs, des approximations de la solution exacte de la loi de refroidissement passif sont proposées dans la section 5.3.6, cette dernière se révélant être une équation assez complexe. L'emballement thermique de l'équation de la chaleur passive appliquée à un modèle de microprocesseur réaliste est également étudié.

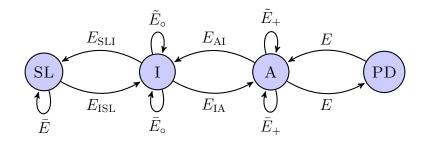

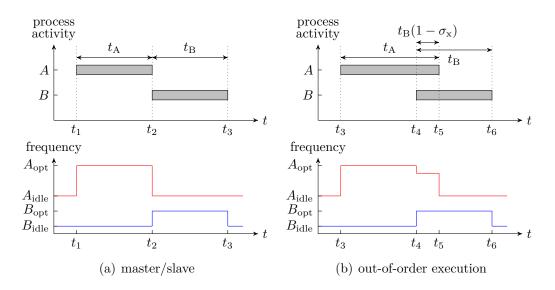

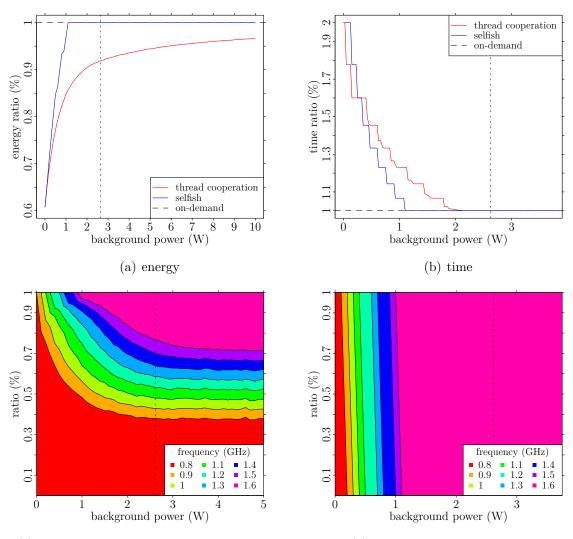

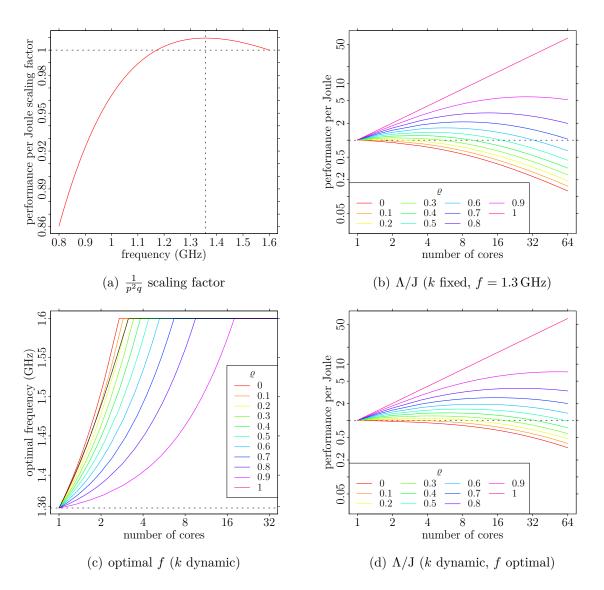

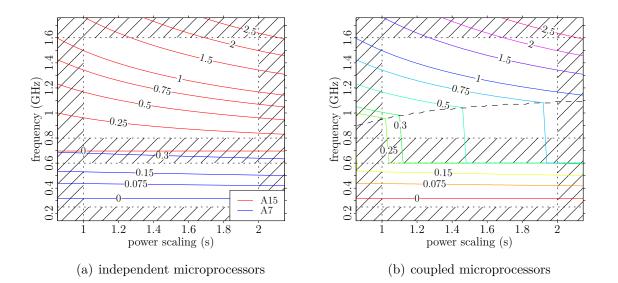

### Applications aux domaines multi-horloge de la consommation optimale d'énergie

La loi de convexité énergie-fréquence de la consommation des programmes du chapitre 4 est appliquée à des cas d'usage spécifiques dans ce chapitre. Les systèmes d'agents coopérants sont étudiés dans la section 6.1, et une solution analytique est développée pour trouver la fréquence d'horloge optimale pour tous les participants, dans le but de minimiser la consommation énergétique globale de l'ensemble du système. Il est démontré que, pour trouver la fréquence optimale pour chaque participant, la règle de convexité doit être appliquée de nouveau chaque fois que le système change son état d'énergie. Dans la section 6.2, la règle de convexité est appliquée à un système soumis à des contraintes temporelles. Les résultats montrent que l'on peut économiser jusqu'à 55% de l'énergie, dans le meilleur des cas. Mais ces économies peuvent devenir marginales lorsque beaucoup de travail doit être effectué avant la date limite. La section 6.3 examine si l'application de la règle de convexité peut conduire à économiser de l'énergie par ajustement de la fréquence d'horloge de threads parallèles individuels. Il sera montré que, pour une consommation d'énergie de fond comparable à la consommation d'énergie du microprocesseur, des économies d'énergie entre 3% et 10% par rapport à la consommation énergétique induite par le gestionnaire de fréquence d'horloge typiquement mis en œuvre par Linux sont possibles. La section 6.4 intègre la notion d'énergie dans la loi d'Amdahl pour analyser la performance par Joule d'un microprocesseur. On montre comment la fréquence d'horloge qui minimise la consommation d'énergie se comporte sous la loi d'Amdahl. Dans la section 6.5, on s'attache à démystifier les relations qu'on suppose traditionnellement entre calcul hétérogène et énergie. Le contraste entre le comportement d'un microprocesseur

basse-puissance et un autre à haute performance est mis en évidence en utilisant la loi de convexité énergie-fréquence de la consommation des programmes et la loi de Amdahl. Une taxonomie spécifique est introduite pour distinguer les différentes facettes de la notion de puissance.

### Conclusions

#### Résumé des résultats

Dans ce travail, la loi de convexité énergie-fréquence de la consommation des programmes est établie analytiquement et validée par une vast bibliographie ainsi que des mesures expérimentales. La thermosensibilité de la loi de convexité énergie-fréquence de la consommation des programmes et le profil de puissance des microprocesseurs ont également été discutés. En outre, des procédés pour améliorer la précision des mesures de l'énergie et de la puissance ont été présentés.

La loi de convexité énergie-fréquence de la consommation des programmes s'applique à un système informatique dont la consommation d'énergie  $E_{sys}$  peut être décrite par:

$$E_{\rm sys} = \left( \left(1 + \gamma V\right) \xi f V^2 + P_{\rm back} \right) \cdot cc_{\rm b} \left( \frac{1}{f - f_{\rm k}} + \beta \right), \tag{4.2}$$

où :  $\gamma$  est un paramètre associé aux courants de fuite ; V est la tension du processeur ;  $\xi$  est la demande de puissance du processeur ; f est la fréquence d'horloge du processeur ;  $P_{\text{back}}$  est la demande de puissance du système, excepté celle du processeur ;  $f_k$  sont les *voleurs de temps* (temps d'attente typiquement sur des entrées/sorties); et  $\beta$  est le *slack time* du processeur (du au fonctionnement du système).

$$E_{n} = E_{n}^{A} + E_{n}^{B}$$

$$\frac{\partial E_{n}^{A}}{\partial f} = (4af^{3} + 3bf^{2} + 2cf + d) \cdot \beta$$

(11.a)

$$\frac{\partial E_{n}^{B}}{\partial f} = \frac{3af^{4} + (2b - 4af_{k})f^{3} + (c - 3bf_{k})f^{2} + 2cf_{k}f + (P_{back} - df_{k})}{(f - f_{k})^{2}}$$

(11.b)

$$\frac{\partial^2 E_{\rm n}^{\rm A}}{\partial f^2} = (12af^2 + 6bf + 2c) \cdot \beta \tag{11.c}$$

$$\frac{\partial^2 E_{\rm n}^{\rm B}}{\partial f^2} = \frac{-6af^4 + (16a\,f_{\rm k} - 2bc\,f_{\rm k}^2)f^3 + (6b\,f_{\rm k} - 12a\,f_{\rm k}^2)f^2}{(f - f_{\rm k})^3} - \frac{6b\,f_{\rm k}^2 f + 2(d\,f_{\rm k} + P_{\rm back})}{(f - f_{\rm k})^3} \tag{11.d}$$

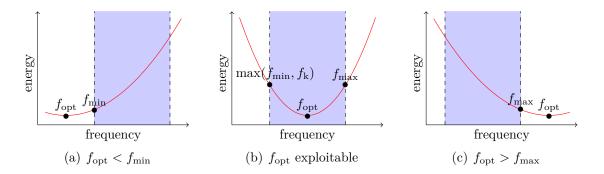

Si la dérivée première de l'énergie  $E_n$  a une seule racine sur  $\mathbb{R}^+$  et la dérivée seconde est une fonction croissante monotone, alors la consommation d'énergie du système présente un minimum global avec à une valeur optimale de la fréquence d'horloge  $f_{opt}$ . Par définition, cette fréquence d'horloge optimale donne la plus petite consommation d'énergie pour l'exécution d'une séquence d'instructions. Si la fréquence d'horloge optimale se situe dans la plage des fréquences d'horloge admissibles du microprocesseur, elle peut être exploitée. Dans le cas contraire, le microprocesseur est le plus économe en énergie pour une fréquence d'horloge se trouvant en limite de plage : la fréquence maximale ou minimale de l'horloge. La consommation d'énergie est une fonction de plusieurs paramètres: les demandes en puissance du microprocesseur  $(\xi)$ , les capacités d'adaptation tension / fréquence (f/V), la consommation de base  $(P_{\text{back}})$ , le slack time  $(\beta)$ , les voleurs de cycles d'horloge  $(f_k)$ , la température T, et quelques autres.